コンピュータシステムの理論と実装 ブール論理

ブール論理

ブールゲートと呼ばれる単純な回路について。参考: コンピュータシステムの理論と実装

ブール代数

ブール代数はブール値(1/0、true/false、真/偽など)が使われる。

正準表現

どのようなブール関数でも、少なくともひとつの正準表現(canonical representation)と呼ばれるブール式で表すことができる。

論理ゲート

ゲート(gate)はブール関数を実装するための物理デバイスである。最も単純なゲートは、あるスイッチ素子を特定の配線回路でつなぎ合わせることで作られる。このスイッチ素子はトランジスタと呼ばれる。別に電気でなくとも、スイッチになるものであればなんでもいいが、電気が一番便利。

ハードウェア記述言語

HDL(Hardware Description Language)という。これを使えば、いちいちAnd、Or、Not回路をハンダ付けせずにソフトウェア上でシミュレーションできる。

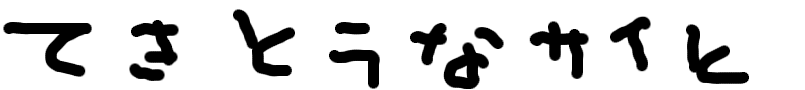

まぁ、とりあえずつくってみよーぜー。xが1の時のみ1を出力する回路をつくるぞー。

XIsTrue.hdlを作成。

CHIP XIsTrue {

IN a, b;

OUT out;

PARTS:

Not(in = b, out = notb);

And(a = b, b = notb, out = w1);

Or(a = a, b = w1, out = out);

}

XIsTrue.cmp。比較対象のファイル。

| a | b |out|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

テストスクリプト。XIsTrue.tstというファイル名で保存。

load XIsTrue.hdl,

output-file XIsTrue.out,

compare-to XIsTrue.cmp,

output-list a b out;

set a 0, set b 0,

eval, output;

set a 0, set b 1,

eval, output;

set a 1, set b 0,

eval, output;

set a 1, set b 1,

eval, output;

Runのボタンを押して、下に「End of script - Comparison ended successfully」とでればよし。 もしでなかったら、XisTrue.outが出力されてるはずなので参照する。

一覧

- コンピュータシステムの理論と実装 ブール論理

- コンピュータシステムの理論と実装 ブール論理のつづき

- コンピュータシステムの理論と実装 ALUの実装

- コンピュータシステムの理論と実装 レジスタとメモリとカウンタ

- コンピュータシステムの理論と実装 機械語

- コンピュータシステムの理論と実装 CPU

- コンピュータシステムの理論と実装 コンピュータそのもの

- コンピュータシステムの理論と実装 アセンブラ

- コンピュータシステムの理論と実装 バーチャルマシン#1

- コンピュータシステムの理論と実装 バーチャルマシン#2